Accelerating simulations with TLM models |

| Our core expertise and focus on SOC design & software, hardware design capability makes us unique in the area of high-level modelling . Our expertise in SystemC based SOC modelling enables our customers to design highly complex SOCs with cost effective way. |

Embedded Processor Modelling |

| With today's system-on-chip (SoC) designs getting highly complex, it puts increased necessity of developing system level simulations. The SoCs include not only the hardware, but the software as well. It becomes extremely important to identify critical hardware/software integration issues early. This, in turn, aids in reducing:

|

|

We, at LogicFab, understand the nitty-gritty of the design and simulation issues, and offer world class services to help you accelerate your hardware simulations.

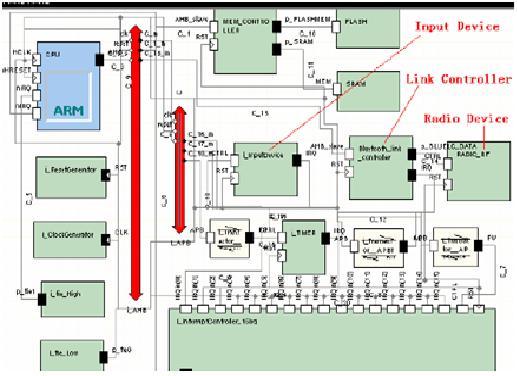

- Various IPs (eg. RAM controllers, Timer, Sleep Counter, GPIO, etc… to name a few)

- RISC based CPUs

- DSP based CPUs

- Bluetooth Low Energy Stack

|

|

|

The TLM is a well-established methodology for modeling complex systems. It is based on SystemC IEEE 666 standard, which is an open source C++.

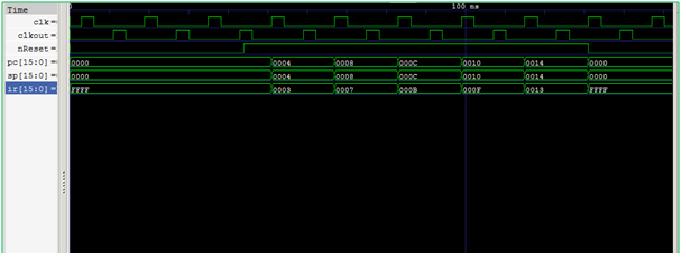

Our Embedded SystemC TLM Processor Models use Instruction Set Simulators (ISS) to emulate the behavior of the processor model. As it is an abstract view of the RTL, the simulation performance achieved is much faster than the hardware model itself. This enables hardware and software designers to share results and thereby refine the design.

|

| We also offer development of Virtual Platforms solutions for the embedded processor models, which are register accurate and are functionally complete. The VP models are available much earlier than the actual RTL, and are accurate enough to be used post-RTL. |

Peripheral Simulation

We also offer creation of peripheral models, which helps in hardware and software co-design and design exploration. These SystemC TLM based models offer reuse of these peripherals across various communication protocols.

|

|

The TLM models offer:-

- TL4 and TL3 abstraction levels

- Further refined for lower abstraction levels (TL2, TL1)

|